Хардуерно внедряване на двоична напълно цифрова фазова заключена система

Системите с фазова блокировка (PLL), направени в напълно цифрова версия, тоест без използването на аналогови елементи като нискочестотни филтри (LPF) и осцилатор с контролирано напрежение (VCO), се използват широко в много LSI за телекомуникации, където се изисква възстановяване на часовника.честота на предавателната система. Липсата на дискретни аналогови компоненти в такава схема позволява да се постигне висока повторяемост на параметрите и същевременно по-ниска цена на блока за управление на честотата.

Разглежда се типичен пример за изпълнение на възел на изцяло цифрова фазова заключена система (PTSPLL, английска нотация - DPLL) на програмируем логически LSI (FPGA) от Altera. Описанието на хардуерната част на езика Verilog ви позволява лесно да прехвърлите възела към FPGA на други производители, например Xilinx, Actel и Lattice.

В предишна статия ("Чип новини", ╧ 9, 2002, стр. 16), блок-схемата на PCFLF беше разгледана подробно и беше направен анализ на широко използваните последователни филтри на цикъла, които служат за повишаване на имунитета срещу шум на системата. Там е описан и филтър за произволно ходене с променлива стойност за нулиране, чието използване позволява да се постигнат добри динамични характеристики на контура, без да се губи имунитет. По-долу ще разгледаме изпълнението и прилагането на такъв възел в реална система.

В процеса на работа с телекомуникационно оборудване стана необходимо да се свърже оригиналният модул за обработка на сигнала към сигналните линии на интерфейса ISDN-BRI в точка S, който отговаря на спецификацията ITU-T I.430. Физическата конфигурация на този интерфейс има един мрежов терминал, два завършващи резистора (единият в мрежовия терминал, другият в края на шината) и осигурява възможност за свързване на няколко терминални устройства към шината [1]. Електрическата спецификация на интерфейса ITU-T G.961 предвижда предаване на битове с данни чрез трикратен код (фиг. 1) с променлива импулсна полярност - биполярен AMI код. Този код има недостатъка, че ако се предаде дълга последователност от тях, разпределението на часовника може да бъде влошено. В някои версии на оборудването, използващо такъв код, данните са специално кодирани, за да се улесни синхронизирането на приемника, но за интерфейса I.430 не е предвидено кодиране. Като се имат предвид практически използваните комуникационни системи, изградени на този интерфейс, може да се гарантира, че в зависимост от състоянието на канала, продължителността на „периода на мълчание“ достига дължината на един кадър. В същото време изискванията на спецификацията установяват недопустимост на десинхронизация на конзолата и главното оборудване дори в случай на "тишина" в линията до 40 кадъра, т.е. 10 ms. По този начин беше необходимо да се изгради възел, който осигурява надеждна синхронизация на приемо-предавателя на крайното устройство с главното оборудване.

Фигура 1. Форма на вълната на основния потребителски интерфейс

Използване на PCSFAPCH за изграждане на възел на синхронизатора

За да се осигури битова синхронизация, тоест да се получи на изхода на възела последователност от импулси, всеки ръб на който, положителен или отрицателен, попада в средата на битовия интервал на входния сигнал, препоръчително е да се използва PDSFAP, който има достатъчна инерция, за да предотврати "отклонение" на фазата на изхода на синхронизатор за предаване на дълга поредица единици. В нашия случай такива интервали могат да достигнат 240 μs, при липса на активирано крайно оборудване в шината. В този случай продължителността на един битов интервал е 5,2 μs, което е еквивалентно на скоростта на предаване на данни с честота 192 kHz. Възможни са и други версии на устройството, като например използването на брояч, рестартиран от ръба на входния сигнал, но такъв синхронизатор няма да има граница на шумоустойчивост и освен това е много взискателен за точността на задаване на честотата на главния генератор в проектираната система.

Характеристики на включването на PCFAPCH в смесена сигнална верига

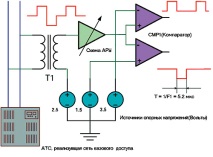

Разглежданото устройство, съдържащо синхронизаторния блок, е аналогово-цифрова схема, при която сигналите, постъпващи на входа от интерфейса на шината, са аналогови, а работата по синхронизиране и разделяне на битовете на входната последователност се извършва от цифрови схеми на стандарта LVTTL или LVCMOS. За да се свържат нивата на сигнала на интерфейса, използван с логическите нива на цифровата част на системата, може да се използва аналогово-цифров преобразувател, когато се използва процесор за цифров сигнал (DSP) в по-нататъшната обработка, или сравнителен който разделя положителните и отрицателните импулси на троичния AMI код. В описания възел използването на DSP е излишно и схемата, показана на фиг. 2. Потенциалите на заземяване на оборудването, което осъществява мрежовото прекратяване, и наземните потенциали на терминалното оборудване могат да се различават, освен това често се предава постоянно напрежение върху двойките сигнали на интерфейса за захранване на терминалите. Поради тези причини входният сигнал, за да се избегне нежеланото влияние на общото напрежение, се подава към изолационния трансформатор Т1, след което положителните и отрицателните импулси от нивото на LVTTL се разпределят върху компаратора СMP1, който може да бъде приложени директно към входа на синхронизатора. Схемата AGC не е задължителна, но нейното използване е подходящо, когато нивата на сигнала на предавателите в шината са нестабилни или неизвестни предварително, което може да е следствие от затихване в нискокачествената линия.

Фигура 2. Схема за разделяне на еднополюсни импулси от линеен AMI код

Хардуерно внедряване на PCFAPCH в синхронизатора

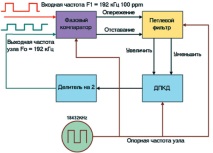

На фиг. 3 показва блок-схема на единица, която включва синхронизатор. Инсталираната в модула микросхема ACEX EP1K50TC144 успешно направи възможно реализирането на осем синхронизиращи възела с необходимата скорост.

Фигура 3. Блок-схема на модула за извличане на честота на синхронизация

Първоначалната задача беше да се възстанови синхронизацията на часовника с честота F1 = 192 kHz. В този случай честотата на тактовия сигнал, подаван към програмируемата логическа LSI, е избрана да бъде кратна на F1 и достатъчно висока, за да осигури малко количество фазово трептене. Също така, по време на анализа на закъсненията в CAD системата "MAXPlus + II Baseline" беше открита максималната честотна граница отгоре. В резултат на това оптималната честота на синхронизаторния блок беше 18432 kHz, което е 96 пъти по-висока от честотата на предаване на данни през шината на обслужвания интерфейс. Избрахме базовия коефициент на делителя с променливо съотношение на деление (VDP) да бъде два пъти по-малък, т.е. 48. Това се дължи на желанието да се получи сигнал на изхода с работен цикъл 2.

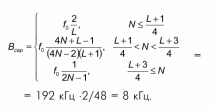

За това делителят на 2 се включва веднага след изхода на DPKD. Това решение не е задължително и ако не бъде приложено, коефициентът на разделяне L ще бъде равен на 96, което обаче ще намали трептенето в замяна на намаляване на честотната лента на придобиване. Следователно стъпката на корекция се оказа равна:

TC = 2/18432 kHz = 1.09╥10 -7 s.

По този начин ширината на лентата за задържане на възела е:

което е около 4% от базовата честота F1 = 192 kHz и много повече от нестабилността, определена от I.430 (8.1.2) [3].

Широчината на улавяне за дълбочина на филтъра на контура N = 8 и честота на отворен контур f0 = 192 kHz:

Възелът отговаря на изискванията на параграф 8.2.2 от спецификацията [3], който определя приемливите граници за фазово трептене на възстановения сигнал за синхронизация в рамките на 7%, което беше ясно отразено в предишната статия.

Фазовият компаратор сравнява фазата на тактовия изход и последователността от данни на интерфейса при всеки положителен ръб на входния поток. В този случай компараторът има характеристика на релето [2], което дава печалба в хардуерните разходи, но, от друга страна, увеличава инерцията на управляващия контур, което обаче не е критично в нашия случай. Решението за сравнение на фазите се предава на контурния филтър с дълбочината на съставящия го N-филтър 8 и M-филтър 32. Заключването на сигналите за сравнение на фазите се извършва на положителния ръб на общата референтна тактова честота на възела (MainClock). Имайте предвид, че за надеждната работа на възела всички процеси в модулите се синхронизират с този сигнал, това ви позволява да избегнете недефинирани състояния на регистрите и да постигнете стабилна работа на синхронизатора в различни изпълнения. Цикличният филтър от своя страна генерира положителни и отрицателни сигнали, които контролират фазовото изместване на изходната честота чрез устройството за фазово управление. Последният се основава на брояч, чиято стойност се увеличава с 2 в случай на фазово изоставане и изобщо не се увеличава в случай на аванс. Тези операции напълно съответстват на „вмъкването“ на допълнителен импулс или „изтриването“ в случай на използване не на DPKD, а на разделител с фиксирано съотношение на разделяне. При липса на сигнали за фазово управление стойността на нарастването на брояча е равна на единица и в този случай стационарната честота на изхода на контура ще бъде равна на

f0 = 18432 kHz/2╥48 = 192 kHz

Общият изглед на системата с FPGA, ресурсите на която са внедрени от PCFAPCH възела, е показан на фиг. 4.

Фигура 4. Фрагмент от модула, който включва възела за синхронизация

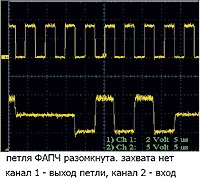

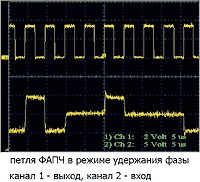

Практическият резултат е тестван върху инсталиран хардуер, който поддържа основен потребителски интерфейс, който отговаря на спецификацията ITU-T I.430 и е показал, че системата е напълно работеща. Когато цикълът е отворен (например, въвеждането на последователността от данни е късо към земята), не настъпва никакво регулиране и входните данни свободно се "плъзгат" по изходния часовник (фиг. 5). В случай на затворен цикъл, възелът улавя фазата на входния сигнал, като всеки падащ ръб на изходната честота попада в средата на битовия интервал на данни, предадени през шината (фиг. 6). Освен това тази честота може да се използва за фиксиране на входящите битове и тяхната последваща обработка.

- PayPal - нови функции на платежната система

- Внимание Нова система за изработка! 23 ноември 2010 г.

- Хардуерно оформяне на тялото Slim Up - кавитация

- Пещерна система Воронцов

- Изчерпателна проверка на градската система за предупреждение ще се проведе в Санкт Петербург - Администрация