Повече за метастабилността

Хардуерен проект с отворен код

Повече за метастабилността.

Искам да говоря за един проблем, който често се среща при разработването на цифрови устройства, но за съществуването на който много хора забравят или дори не подозират.

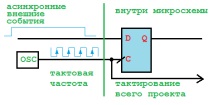

Нашите проекти за FPGA са цифрови, повечето процеси в него се извършват синхронно с тактовата честота на свързания генератор. Въпреки това, самата микросхема получава сигнали от външния свят и често тези сигнали са асинхронни на нашата тактова честота.

Тук са възможни проблеми.

Да предположим, че искаме да „хванем“ външно събитие с помощта на D спусък. Такъв спусък запомня сигнала на входа д и го издава на изхода Въпрос: в момента на положителен ръб (отпред) на сигнала на входа ° С .

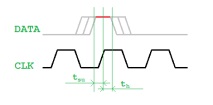

За съжаление (или може би за щастие) нещата не се случват моментално в реалния свят. Самата предна част на часовника е леко разтегната във времето и спусъкът не се превключва незабавно, необходимо е време за превключване. За да фиксирате успешно входната стойност в D-тригера, входният сигнал трябва да бъде стабилен за известно време преди ръба и след ръба на тактовата честота. Тези времена се наричат цу (време за настройка) и ти (време на задържане).

Тъй като входният сигнал, който разглеждаме, е асинхронен на тактовата честота, има вероятност сигналът да започне да се променя по време на фронта на тактовата честота. Такъв е случаят, когато времената не се спазват цу или ти . На изхода на спусъка няма да бъде фиксирана нула и не една, а някаква междинна стойност.

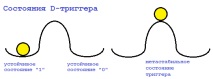

Това състояние е много нестабилно. Известно е, че спусъкът не може да остане в това състояние дълго време. Вероятността тригер да напусне метаболитното състояние нараства експоненциално с времето.

По принцип самият спусък излиза от метастабилното състояние след известно време. tres (време за разделителна способност) поради собствения си вътрешен шум. Така че е въпрос на време.

Има определена сложна формула, която ви позволява да прецените колко често се случва събитие с метастабилност. Има такава концепция MTBF (Средно време между отказите) - време между "отказите".

- Fevent - честота на входните събития.

- Fclk - тактова честота на спусъка.

- tres - времето, когато спусъка напусне метастабилното състояние (време на разделителна способност), зависи от технологията на производството на микросхемата.

- tff и Kff - също коефициентите, свързани с технологията за производство на логически елементи и задействания в микросхема.

За да се намали влиянието на възможната метастабилност, в схемата на устройството се въвеждат синхронизатори. Всъщност те са само два последователни тригера.

Ако първият задействащ сигнал „хване“ метастабилното състояние, тогава той вероятно трябва да премине по времето, когато сигналът е фиксиран във втория задействащ механизъм. Ясно е, че този метод не премахва напълно възможните проблеми, но значително намалява вероятността от метастабилно състояние във втория тригер. След втория спусък можем уверено да предположим, че сигналът винаги ще бъде стабилен (или "0", или "1").

Нека разгледаме проблема от практическа гледна точка. Използваме FPGA от Altera и използваме неговата среда за разработка Quartus II. Има ли диагностични инструменти за метастабилни състояния? Може би има инструменти за анализ на проектите за качество?

Оказва се, че има такъв диагностичен инструмент: Design Assistant. Изберете Задания/Настройки ... от менюто на околната среда Altera Quartus II.

Сега нека направим прост проект:

Започваме компилация и виждаме, че компилаторът не издава никакви допълнителни специални предупреждения. Това се дължи на факта, че той се надява, че входният сигнал данни все още е синхронен със сигнала клик .

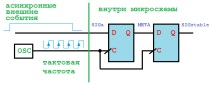

Сега усложняваме проекта:

Сега компилаторът не може да има съмнения относно естеството на входните сигнали. Сигнал на часовника клик преминава към първия спусък и другия сигнал на часовника clk2 отива към втория спусък. Проектът има две тактови честоти. Ако входният сигнал данни фиксиран в първия спусък от тактовата честота клик, ясно е, че за втория спусък той ще дойде асинхронен по отношение на честотата clk2 . Данните се предават от една част на веригата, където работи честотата клик, към друга част от веригата, където работи друга честота clk2 . В чуждестранната литература този факт се нарича Crossing Clock Domains. .

Започваме да компилираме проекта и виждаме съобщението от Design Assistant:

Критично предупреждение: (Високо) Правило D101: Битовете за данни не се синхронизират, когато се прехвърлят между асинхронни часовникови домейни. (Определена стойност: 2). Намерени са 1 асинхронна структура (и) на интерфейс на домейн с часовник, свързани с това правило.

По този начин Quartus II ни казва, че не всичко е добре в проекта.

Добавете още един спусък (синхронизатор) към проекта:

Ние компилираме и сега няма повече критично предупреждение от Design Assistant. По този начин се препоръчва да се направи преход на сигнал от един домейн на часовника към друг.

Заключение:

- Колкото по-бърза е микросхемата, толкова по-малка е вероятността за метастабилно състояние, когато асинхронен сигнал е фиксиран в спусъка, тъй като неговите параметри цуи ти по-малко от по-бавния чип.

- Колкото по-висока е тактовата честота на задействането и колкото по-висока е честотата на асинхронни входни събития, толкова по-вероятно е да възникне метастабилно състояние.

- Когато прехвърляте данни от един домен на часовник към друг, е задължително да използвате синхронизатори - два (или повече) тригера в серия.

- Използването на тригери на синхронизатори въвежда забавяне в предаването на сигнала, но просто трябва да се примирите с това и да го вземете предвид по-късно в проекта.

- Един асинхронен сигнал трябва да бъде синхронизиран с проектния часовник само веднъж.

- Етикети:

- Кръстоса на домейн на часовника

- MTBF

- синхронизатор

- синхронизатор

- Как да укрепим покривната конструкция на къщата

- Как да отрежа детски блог за коса My BeTeshka

- Как да изберем улично осветление

- Диагностика на кръвен тест за паразити, биологични среди

- Как да изберем ютия за дома си, 1000 тайни